Компания Samsung Electronics, один из крупнейших мировых

производителей динамической оперативной памяти (dynamic random access

memory, DRAM), объявила о своих планах касательно развития направления

многослойной кубической памяти (multi-layer hyper memory cube, HMC).

Согласно этим планам к концу 2012 года должен быть выработан единый

отраслевой стандарт, а массовое производство памяти HMC должно начаться в

2013-2014 году.

Память HMC разрабатывается для того, что бы прорваться сквозь узкое

место современных вычислительных систем, называемое "барьером памяти

/memory wall", которое в настоящее тормозит развитие многоядерных,

многозадачных микропроцессорных систем.

"Барьер памяти" представляет собой противоречие, вызванное разницей

между скоростями работы центрального процессора и системой памяти,

расположенной за пределами чипа. Основную роль в возникновении этого

противоречия играет ограниченная пропускная способность внешних шин

данных, по которым осуществляется передача информации в и из памяти. За

период с 1986 по 2000 год скорости центральных процессоров увеличились в

среднем на 55%, а скорость работы памяти за этот период выросла всего

на 10%, что только усугубило ситуацию с "барьером памяти".

"Мы ожидаем, что наша группа закончит разработку единого отраслевого

стандарта для первого варианта реализации памяти HMC к концу 2012 года. В

течение года или двух после этого первые продукты на базе HMC должны

достичь потребительского рынка и составить конкуренцию памяти DRAM в

мобильных устройствах, компьютерах и сетевом оборудовании" - поделился

планами компании Джим Элиот (Jim Elliott), вице-президент Samsung по

американскому региону.

Компании Micron и Samsung сформировали консорциум HMCC (hybrid memory

cube consortium), который будет тесно сотрудничать с другими компаниями,

такими как Altera Corp., Open-Silicon и Xilinx, в деле разработки

спецификации нового типа памяти, разработки единых технологических

процессов ее производства. Помимо этого на пути внедрения нового типа

памяти потребуется и участие ведущих производителей наборов компьютерной

логики, так называемых чипсетов, ведь преодоление "барьера памяти"

потребует не только самой новой памяти, но и изменений в архитектуре

вычислительных систем.

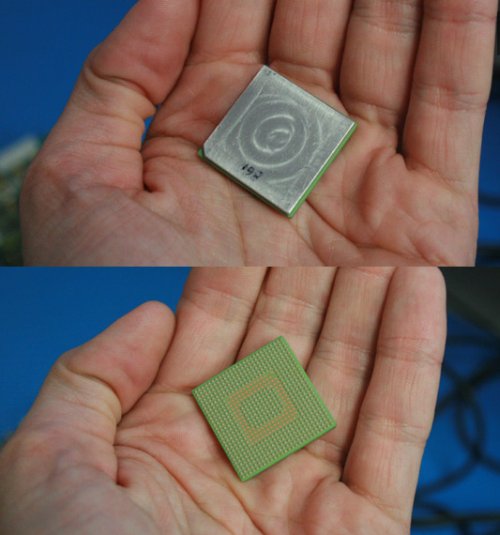

Определенные шаги в этом направлении предпринимает компания Intel

Corp., представители которого на проходившем в сентябре месяце форуме

Intel Developer Forum продемонстрировали опытные образцы Hybrid Memory

Cube, разработанные совместными усилиями специалистов Intel и Micron.

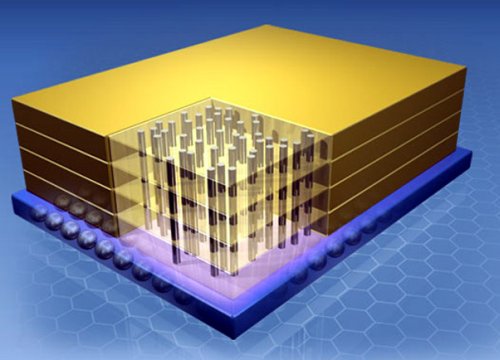

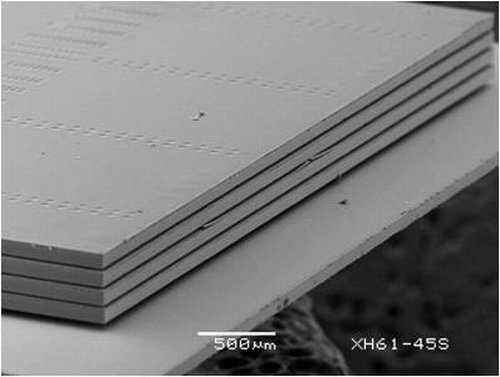

Память Hybrid Memory Cube демонстрирует совершенно новый подход к

созданию чипов памяти, помимо этого, по сравнению с памятью DDR3 новая

память показывает семикратное увеличение энергоэффективности. Память

типа Hybrid Memory Cube представляет собой уложенные в "штабель" обычные

чипы памяти, формирующие компактную кубическую структуру. Такая

структура динамической памяти может обеспечить скорость передачи

информации вплоть до 1 Тбит/с, что может вывести на совершенно новый

качественный уровень серверные системы, предназначенные для построения

систем "облачных" вычислений, планшетные, мобильные компьютеры и

смартфоны.